238層 4D NAND開発成功

- 世界初の238層512Gb(ギガビット)TLC(Triple Level Cell)を

7月開発完了、来年上半期に量産開始 - 最高層、最小面積製品の実現、生産性/速度/消費電力を画期的な改善

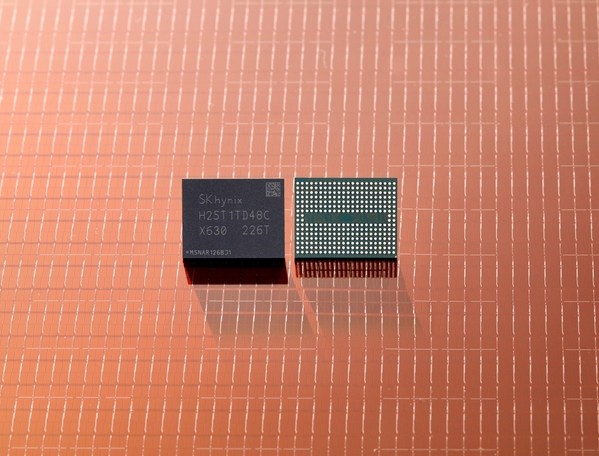

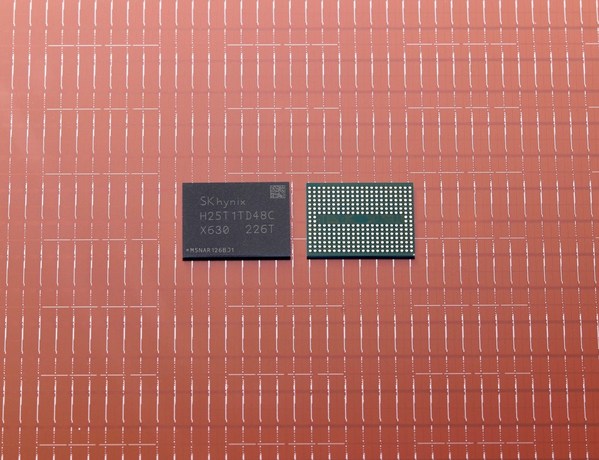

ソウル、2022年8月3日 PR Newswire– SKハイニックス(www.skhynix.com )は本日、現存最高層となる238層NAND開発に成功したと発表しました。

SKハイニックスは最近238層512Gb(ギガビット)TLC(Triple Level Cell)* 4D NANDフラッシュメモリサンプルの出荷を顧客向けに開始し、来年上半期に量産体制に入る予定です。当社は、2020年12月に176層NANDを開発してから1年7ヶ月ぶりに次世代技術開発に成功致しました。特に、今回の238層NANDは世界最高層でありながら世界で最も小さいサイズを実現したという点が重要な意味を持ちます。

*NANDフラッシュメモリは、1つのセル(Cell)に何個の情報を保存するかによって、SLC(Single Level Cell、1個)- MLC(Multi Level Cell、2個)- TLC(Triple Level Cell、3個)- QLC(Quadruple Level Cell、4個)- PLC (Penta Level Cell, 5個)などで規格が分かれています。情報の保存量が増えるほど、同じ面積に多くのデータを保存できます。

SKハイニックスは当日、米サンタクララで開幕した「フラッシュメモリーサミット(FMS : Flash Memory Summit)2022」*で238層NAND新製品を公開致しました。 崔正達(チェ・ジョンダル)SKハイニックス副社長(NAND開発担当)はFMSイベントの 基調演説で、「当社は4D NAND技術力を土台に開発した238層NANDを通じて、コスト、性能、品質の面でグローバルトップクラスの競争力を確保しました。 今後も技術限界を突破するために革新と挑戦を続けて参ります」と述べました。

*フラッシュメモリーサミット(FMS : Flash Memory Summit) : 毎年、米カリフォルニア州サンタクララで開かれるNANDフラッシュメモリ業界で世界最大規模のカンファレンス(Conference)。SKハイニックスはNANDソリューション子会社であるSolidigmと今年のFMS基調演説で共同発表を行いました。

SKハイニックスは2018年に開発した96層NANDから、従来の3Dを超えた4D製品を披露してきました。 4次元構造でチップが具現される4Dを作るために、当社の技術陣はCTF(Charge Trap Flash)*とPUC(Peri Under Cell)*技術を適用しました。 4Dは3Dに比べて単位当たりのセル面積が減りながらも生産効率が高くなるメリットがあります。

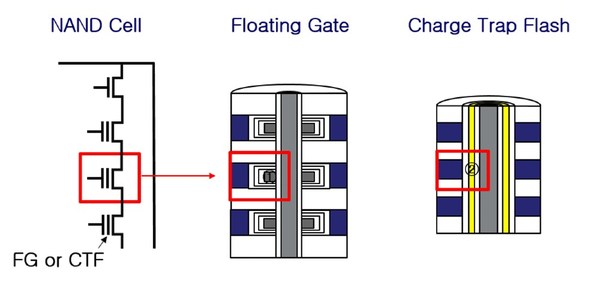

* CTF (Charge Trap Flash)

電荷を導体(1)に保存するフローティングゲート(Floating Gate)とは異なり、電荷を不導体(2)に保存してセル間干渉問題を解決した技術で、フローティングゲート技術より単位当たりのセル面積を減らしながらも読み書き性能を高めることができるのが特徴。

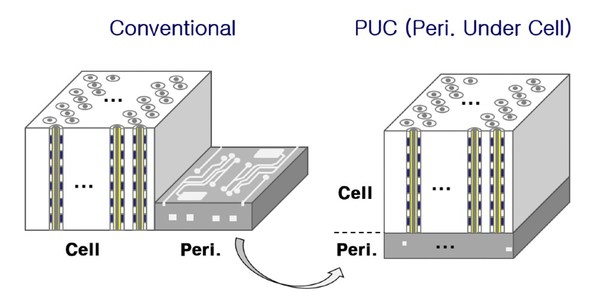

* PUC (Peri Under Cell)

周辺部(Peri.)回路をセル回路下端部に配置して生産効率を極大化する技術

今回の238層NANDは層が増えただけでなく、世界最小サイズで作られ、前世代の176層NANDと比べて生産性が34%高くなりました。これは以前より単位面積当たりの容量が大きくなったチップがウェハー当たりより多くの個数で生産されるためです。

これと共に、238層NANDのデータ伝送速度は1秒当たり2.4Gb(ギガビット)で、以前世代より50%速くなりました。また、チップがデータを読む時に使うエネルギー使用量が21%減り、消費電力節減を通じてESGの観点からも成果を上げたと当社は見ています。

SKハイニックスはPC保存装置であるcSSD(client SSD)に搭載される238層NAND製品を先に供給し、その後スマートフォン用とサーバー用高容量SSDなどに製品活用範囲を広げていく計画であり、続いて来年には現在の512Gb(ギガビット)より容量を2倍増加させた1Tb(テラビット)製品も披露する予定です。